- Čeština

-

EnglishDeutschItaliaFrançais한국의русскийSvenskaNederlandespañolPortuguêspolski繁体中文SuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикGalegolietuviųMaoriRepublika e ShqipërisëالعربيةአማርኛAzərbaycanEesti VabariikEuskeraБеларусьLëtzebuergeschAyitiAfrikaansBosnaíslenskaCambodiaမြန်မာМонголулсМакедонскиmalaɡasʲພາສາລາວKurdîსაქართველოIsiXhosaفارسیisiZuluPilipinoසිංහලTürk diliTiếng ViệtहिंदीТоҷикӣاردوภาษาไทยO'zbekKongeriketবাংলা ভাষারChicheŵaSamoa日本語SesothoCрпскиKiswahiliУкраїнаनेपालीעִבְרִיתپښتوКыргыз тилиҚазақшаCatalàCorsaLatviešuHausaગુજરાતીಕನ್ನಡkannaḍaमराठी

Vysvětlení ASIC: Porovnání designu, typů a GPU

Katalog

Průzkum čipů ASIC v roce 2026

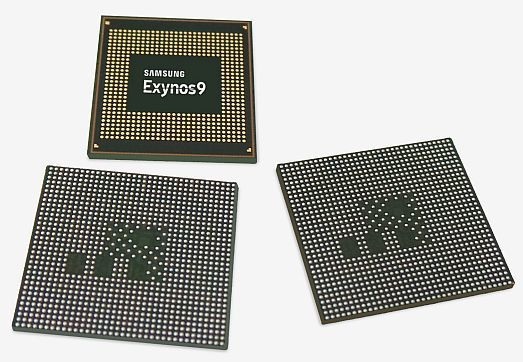

Integrované obvody specifické pro aplikaci neboli ASIC jsou vlastní čipy vytvořené tak, aby vykonávaly specifické úkoly namísto toho, aby zpracovávaly mnoho obecných výpočetních funkcí.V roce 2026 jsou ASIC široce používány v AI, kryptografii, automobilových systémech, edge computingu a vysoce výkonné elektronice, protože nabízejí rychlejší zpracování, nižší spotřebu energie a lepší efektivitu pro cílené pracovní zatížení.

Na rozdíl od univerzálních procesorů jsou ASIC navrženy kolem jedné hlavní funkce.Díky tomu jsou užitečné pro úkoly, které vyžadují rychlost, přesnost a stabilní výkon, jako je inference AI, zpracování transakcí blockchain, komunikace 5G a autonomní řízení vozidel.Jejich specializovaný design pomáhá snižovat latenci a plýtvání energií a zároveň zvyšuje spolehlivost v náročných systémech.

Moderní ASIC také těží z pokročilých polovodičových technologií.Novější procesní uzly, čipletové architektury, paměť s vysokou šířkou pásma, vestavěná správa napájení a bezpečnostní funkce na čipu umožňují ASIC zpracovávat velké množství dat v kompaktním a efektivním designu.Díky těmto vylepšením jsou ASIC důležité v odvětvích, kde záleží na výkonu, energetické účinnosti a zabezpečení.

Celkově ASIC představují posun směrem ke specializovanému hardwaru.Vzhledem k tomu, že obecné škálování procesoru je stále obtížnější, poskytují ASIC praktický způsob, jak zlepšit výpočetní výkon pro konkrétní aplikace.

Pracovní postup návrhu ASIC

Pracovní postup návrhu ASIC je proces krok za krokem, který se používá k přeměně vlastního nápadu čipu na vyrobitelný produkt.V roce 2026 tento proces často využívá nástroje Electronic Design Automation poháněné umělou inteligencí ke zlepšení rychlosti, přesnosti a optimalizace návrhu.

Proces obvykle začíná plánováním architektury.Inženýři definují hlavní funkce čipu, jako jsou jádra AI, řadiče paměti, síťová rozhraní nebo bezpečnostní bloky.Stanovují také cíle pro výkon, výkon a oblast, aby se ujistil, že čip vyhovuje zamýšlené aplikaci.

Následuje návrh logiky, kde inženýři popisují, jak by měl čip fungovat, pomocí jazyků pro popis hardwaru, jako je Verilog nebo VHDL.Tato fáze vytváří návrh RTL, který vysvětluje, jak se data pohybují čipem a jak se každý logický blok chová.

Poté ověření před výrobou zkontroluje, zda návrh funguje správně.Simulace, emulace FPGA a digitální testování pomáhají identifikovat chyby, problémy s časováním, problémy s napájením a případy okrajů.Tento krok je důležitý, protože oprava chyb po výrobě je velmi nákladná.

Fáze fyzického návrhu převádí návrh logiky na skutečné rozložení čipu.Inženýři umísťují bloky obvodů, připojují vodiče, řídí časování, snižují úniky energie a připravují návrh pro zvolený výrobní proces.

Nakonec se návrh dostane na pásku, kde je hotový layout odeslán k výrobě.Po vyrobení může čip projít testováním, balením a validací, než bude použit ve skutečných produktech.

Posouzení ASIC versus GPU: Silné stránky a výzvy

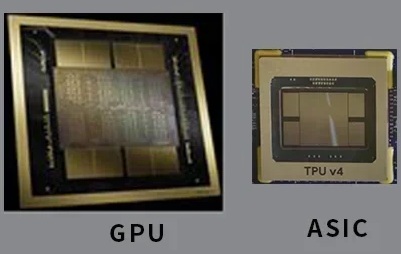

ASIC (Application-Specific Integrated Circuits) jsou účelově vytvořeny pro jednofunkční úlohy a obsahují vyhrazenou hardwarovou logiku pro provádění specifických operací s vysokou účinností.Naproti tomu grafické procesorové jednotky (GPU) fungují jako flexibilní paralelní výpočetní stroje, zběhlé ve zvládání různorodých a náročných pracovních zátěží.Rozdíl v jejich designérských filozofiích definuje jejich příslušné silné stránky a kompromisy a zdůrazňuje rozhodnutí potřebná při výběru mezi těmito dvěma technologiemi.

Výhody ASIC

ASIC svým designem optimalizují výkon a spotřebu energie pro konkrétní aplikace a přinášejí výsledky, které nemají ve specializovaných pracovních zátěžích obdoby.

• Díky vyloučení komponent typických pro univerzální čipy, jako jsou CPU a GPU, dosahují ASIC výjimečné hustoty čipů.To umožňuje až pětinásobné zmenšení fyzické velikosti v klíčových aplikacích, jako je umělá inteligence.

• Datová centra vybavená ASIC hlásí pokles spotřeby energie, často v rozmezí od 50 % do 70 %.Toto snížení je úhledně v souladu s globálním úsilím o přijetí energeticky účinných systémů a snížení uhlíkové stopy.

• Nižší spotřeba energie se promítá do praktických úspor a provozní účinnosti, jako jsou snížené nároky na chlazení, méně fyzických zdrojů pro infrastrukturu a flexibilita při škálování operací.

ASIC také řeší problémy s latencí v reálném čase:

• Obcházením operací s nadbytečnou pamětí, které mohou omezit výkon GPU během inference v reálném čase, poskytují ASIC odezvu požadovanou v kritických aplikacích.Například průmyslová odvětví závislá na autonomních vozidlech, systémech okamžité detekce podvodů nebo hyperinteraktivních digitálních asistentech oceňují tyto zisky v oblasti odezvy na úrovni mikrosekund.

Ekonomické přínosy se projevují jako výrobní měřítka ASIC:

• I když je počáteční vývoj nákladný, objemová výroba dramaticky snižuje náklady na jednotku, přičemž vyspělé implementace poskytují modely spotřebitelské úrovně s cenou pouhých 0,30 USD.Díky tomu jsou ASIC obzvláště rušivé pro průmyslová odvětví závislá na opakujícím se strojovém učení nebo inferencích.

Zejména provozní specialisté v cloudových prostředích zdůrazňují praktické výhody používání AI ASIC.Tyto systémy generují nižší teplo, vyžadují méně mechanických zásahů, což týmům umožňuje soustředit se na prodloužené inovační cykly nebo škálovat infrastrukturu tak, aby vyhovovala budoucím požadavkům.

Nevýhody ASIC

Vývoj ASIC představuje překážky, které zmírňují jeho jinak významné výhody, zejména pokud jde o náklady, přizpůsobivost a logistická rizika.

• Počáteční náklady na vývoj pokročilých ASIC jsou vysoké a předpokládá se, že se do roku 2026 vyšplhají až na 500 milionů USD u špičkových návrhů. Takto vysoké překážky omezují přístup k průmyslovým odvětvím, která mohou ospravedlnit masovou výrobu pro rozložení nákladů v čase.

• Úspěch při nasazení hardwaru ASIC závisí na spolehlivé předpovědi poptávky.Tento požadavek vystavuje organizace rizikům kolísajících trhů nebo náhlých změn v technologickém prostředí, kde by chybné výpočty mohly způsobit, že významné investice nebude možné získat zpět.

ASIC od přírody postrádají schopnost dynamicky se vyvíjet:

• Když softwarové algoritmy přerostou schopnosti vložené do návrhu ASIC, základní hardware se často stává irelevantním nebo nepoužitelným.Naproti tomu GPU nabízejí adaptabilitu přeprogramovatelných aktualizací softwaru, aby vyhovovaly rychle se měnícímu pracovnímu zatížení.

• Nepružný jednorázový proces návrhu ASIC, trvající 12 až 24 měsíců, představuje nesoulad s průmyslovými odvětvími, jako je hraní her nebo výzkum AI, kde se technologické trendy vyvíjejí ve zrychleném časovém horizontu.Pro srovnání, GPU procházejí čtvrtletními opakovanými aktualizacemi, aby zůstaly v souladu s novými průmyslovými standardy.

Logistické problémy představují další komplikace:

• Výrobní překážky nebo překážky, jako jsou spory o duševní vlastnictví, mohou vykolejit harmonogram projektu.Dokonce i dobře financované organizace se potýkají se zpožděním, které se šíří produktovými kanály, což zvyšuje riziko projektu pro průmyslová odvětví s přísnými požadavky na dodávky.

Aplikace

Rozlišovací faktory mezi ASIC a GPU se jasně projevují v praktických aplikacích, kde jejich nasazení silně závisí na konkrétních potřebách úkolu.

• ASIC vynikají při použití v opakovaných, vysoce předvídatelných operacích, které vyžadují minimální vývoj v průběhu času.Příklady použití zahrnují těžbu bitcoinů, úzce zaměřené úlohy inference AI a optimalizované platformy okrajových počítačů.

• GPU naopak dominují prostředím, kde je flexibilita a inovace prvořadé.Patří mezi ně výzkum strojového učení, průzkumné experimenty s umělou inteligencí, komplexní vykreslovací kanály a aplikace vyžadující zobecněný výpočetní výkon.

Rozhodnutí mezi ASIC a GPU odhaluje jemný tanec mezi specializací a přizpůsobivostí.Organizace zvažující tyto technologie musí brát v úvahu nejen výkonnostní měřítka, ale také posuzovat ekonomické, vývojové charakteristiky a charakteristiky životního cyklu, které definují jejich vlastní průmyslovou nebo provozní strategii.

Debata ASIC versus GPU ve své podstatě osvětluje širší technologický dialog mezi efektivitou a flexibilitou.Tato dynamická souhra nadále utváří způsob, jakým průmyslová odvětví posouvají hranice, vytvářejí příležitosti a přizpůsobují se rychlému technologickému vývoji.Pochopení této rovnováhy nabízí cenné pohledy na trajektorii současných počítačových pokroků a jejich roli při utváření širšího společenského pokroku.

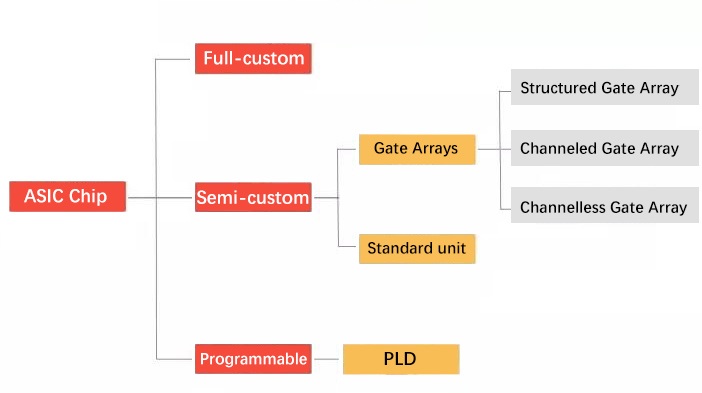

Typy architektur ASIC

Architektury ASIC mohou být organizovány na základě jejich návrhových metodologií nebo aplikačních oblastí.Tyto klasifikace poskytují pohled na nuance technik v polovodičovém inženýrství navržených pro optimalizaci funkčnosti čipů v různých oblastech.Nedávný pokrok odhaluje, že vznikající technologie jsou hnací silou významných transformací v těchto oblastech.

Kategorizace podle metodiky návrhu

Metodika návrhu zařízení ASIC ovlivňuje úroveň jejich optimalizace, celkovou výrobní cenu a vhodnost pro různé aplikace.

• Čipy na zakázku

Úplné návrhy ASIC na zakázku zahrnují pečlivé vytvoření každého tranzistoru a článku pro dosažení nejvyššího možného výkonu a účinnosti.Tato složitá metodika je zvláště cenná pro aplikace vyžadující bezkonkurenční rychlost a přesnost, jako jsou superpočítačové procesory nebo systémy používané ve finančním obchodování, kde nízká latence může přímo ovlivnit ekonomické výsledky.Pečlivá povaha návrhu na míru zajišťuje výjimečné přizpůsobení, ale vyžaduje značný čas a odborné znalosti v oblasti mikroarchitektonického inženýrství.Týmy pracující na takových projektech se často potýkají se složitými technickými výzvami spojenými s ručním návrhem.

• Semi-custom čipy

Polozakázkové návrhy využívají předem otestované „standardní buňky“, což umožňuje inženýrům zaměřit se na uspořádání a funkčnost bez přizpůsobení každého jednotlivého tranzistoru.Tyto ASIC jsou zvláště účinné v odvětvích, jako jsou automobilové systémy nebo průmyslové stroje, kde je nezbytná kombinace spolehlivosti a praktického výkonu.Předstrukturovaná povaha této metodiky zkracuje vývojové cykly a umožňuje výrobcům sladit harmonogramy uvádění produktů na trh s požadavky trhu.Tato rovnováha mezi flexibilitou a efektivitou podporuje pragmatický přístup k vývoji čipů, zvláště když nastanou termíny nebo tlak na škálovatelnost.

• Strukturované ASIC (Legacy Gate Array)

Strukturované architektury ASIC obsahují předem vyrobené tranzistory, které omezují přizpůsobení na propojení.Přestože jejich prevalence poklesla, zůstávají tyto návrhy relevantní pro specializované aplikace upřednostňující střední flexibilitu při nižších nákladech na vývoj.Například některé starší telekomunikační systémy těží ze strukturovaných ASIC díky jejich předvídatelné funkčnosti a vysoké nákladové efektivitě během prodloužené životnosti produktu.Jejich stabilita a nižší složitost poskytují hodnotu v kontextech vyžadujících spolehlivý výkon.

• Programovatelné ASIC (FPGA/PLD)

Programovatelné ASIC, včetně FPGA (Field Programmable Gate Arrays) a PLD (Programmable Logic Devices), jsou základní komponenty během prototypovacích fází vývoje ASIC.Jejich přeprogramovatelná povaha umožňuje iterativní testování a zdokonalování, což je užitečné zejména v raných návrzích, kde úpravy výkonu musí zohledňovat dynamické podmínky reálného světa.Letecké inženýrské týmy často používají FPGA pro optimalizaci algoritmů během zkušebních letů před dokončením projektů ASIC.Adaptabilita programovatelných zařízení vybavuje inženýry k experimentům, aniž by se předčasně zavázali k výrobním specifikacím.

Kategorizace podle aplikace

Klasifikace řízené aplikacemi zdůrazňují, jak klíčová odvětví využívají architektury ASIC k řešení specifických technologických požadavků.

• TPU (Tensor Processing Units)

Jednotky Tensor Processing Unit jsou navrženy tak, aby zvládaly maticové operace, které jsou součástí rámců strojového učení.Jejich schopnost efektivně zpracovávat vysoce výkonné modely je činí neocenitelnými v oblastech, jako jsou simulace autonomních vozidel nebo prediktivní zdravotnické platformy analyzující velké soubory dat.Tím, že poskytují bezprecedentní výpočetní rychlosti a škálovatelnost, TPU nově definují očekávání při trénování modelů AI a komplexní analýze dat.

• LPU (jednotky pro zpracování jazyka)

Jazykové procesorové jednotky jsou optimalizovány pro sekvenční zpracování dat a paměťovou propustnost, díky čemuž jsou ústřední pro úlohy porozumění přirozenému jazyku.Tyto čipy pohánějí aplikace, jako je software virtuálních asistentů schopných sofistikované správy dialogů a analyzátory dokumentů řízené umělou inteligencí používané v právních nebo technických pracovních postupech.LPU vynikají v překlenutí propasti mezi nezpracovaným výpočetním výkonem a vytříbeným kontextovým chápáním.

• NPU (neurální procesorové jednotky)

Neuronové procesorové jednotky jsou přizpůsobeny pro spotřebitelská zařízení provádějící operace umělé inteligence s efektivním využitím zdrojů, včetně rozpoznávání obličeje, analýzy hlasu a intuitivního ovládání gesty.Jednotky NPU zabudované do chytrých telefonů, nositelných technologií a zařízení IoT usnadňují pokročilé funkce, aniž by ohrozily výkon baterie.Jejich integrace odráží širší trendy směrem k decentralizovanému edge computingu, kde zařízení nezávisle provádějí složité algoritmy namísto spoléhání se na cloudovou infrastrukturu.

Architektury ASIC se nadále vyvíjejí spolu s moderními technologickými požadavky.Prostřednictvím specializovaných návrhů uspokojujících různé provozní potřeby inženýři odemykají transformační potenciál napříč průmyslovými odvětvími.Od energeticky účinných systémů IoT až po vysoce výkonná školení AI – tyto zakázkové křemíkové návrhy demonstrují trvalou hodnotu přesného inženýrství.Každá inovace přináší příslib zvýšené funkčnosti zaměřené na řešení stále složitějších výzev.

Průkopnické inovace ASIC nastaveny na předefinování roku 2026

Průmysloví inovátoři neustále zdokonalují technologie ASIC (Application-Specific Integrated Circuit) a pohybují se rychle se vyvíjejícím prostředím s akutním zaměřením na udržení náskoku na konkurenčních trzích.Jejich převratný vývoj významně ovlivňuje odvětví, jako je cloud computing, umělá inteligence (AI), autonomní systémy a spotřební elektronika.Níže jsou podrobně popsána významná vylepšení.

Google TPU v7

TPU v7 od společnosti Google ztělesňuje popředí technologie pro odvození velkých jazykových modelů (LLM) v hyperscale.Jeho sofistikovaná architektura využívá širokopásmová optická propojení spolu s pamětí High Bandwidth Memory (HBM), což umožňuje nepřerušované zpracování v reálném čase při dosažení provozní rovnováhy.Přijetí optických sítí slouží ke snížení latence v distribuovaných systémech, což je zásadní evoluce pro uspokojení rostoucích požadavků na výpočetní techniku AI.Vzhledem k tomu, že aplikace umělé inteligence neustále přetvářejí zapojení lidí a automatizaci, TPU v7 se ukazuje jako nástrojový krok k bezprecedentní škálovatelnosti v porozumění přirozenému jazyku a inteligentnímu nasazení systému.

AWS Trainium 3

Amazon Web Services (AWS) posouvá svou roli v cloudových řešeních umělé inteligence vydáním Trainium 3, čipu šitého na míru pro trénování rozsáhlých modelů umělé inteligence se zvýšenou nákladovou efektivitou.Jeho design optimalizuje souhru mezi výpočetním výkonem a cenovou dostupností a řeší rostoucí prevalenci služeb umělé inteligence, které pohánějí průmysl po celém světě.AWS využívá hluboké odborné znalosti ze své rozsáhlé infrastruktury AI začleněním vylepšení softwaru do Trainium 3, což zajišťuje, že poskytuje jak dostupnost, tak výkon, což je klíčový prvek pro podniky a výzkumné instituce, které se snaží urychlit své schopnosti AI.

Microsoft Maia 100

Společnost Microsoft udělala velké pokroky se svým Maia 100 ASIC, inovativním ústředním prvkem umožňujícím bezproblémový výkon AI napříč platformou Azure a systémy ChatGPT.Základem úspěchů Maia 100 jsou vylepšené datové toky a jemně vyladěné algoritmy, které umožňují vysoce efektivní zpracování různých pracovních zátěží AI, jako jsou konverzační rozhraní, zpracování přirozeného jazyka a prediktivní modelování.Tyto atributy jsou v souladu s vyvíjejícími se požadavky na okamžitou odezvu a výpočetní náročnost napříč špičkovými doménami.

Čip Tesla Dojo

Čip Tesla's Dojo představuje možnosti transformačního zpracování přizpůsobené pro počítačové vidění a autonomní systémy v reálném čase.S pozoruhodnou odezvou při analýze senzorických vstupů a bezkonkurenční efektivitou neuronové sítě podporuje čip pokročilý vývoj v rozpoznávání dopravních vzorů, optimalizaci situační odezvy během jízdy v noci nebo za nepříznivého počasí a adaptivní modely rozhodování.Přehodnocením role ASIC v rámci technologie s vlastním řízením Tesla demonstruje přesvědčivou vizi budoucnosti inteligentní, škálovatelné dopravy.

ASIC zaměřené na spotřebitele

Spotřební elektronika zaznamenala významný pokrok ve funkčnosti umělé inteligence na zařízení, kterou umožňují čipy, jako je Neural Engine od společnosti Apple a Hexagon NPU společnosti Qualcomm.Tyto ASIC optimalizují procesy, jako je rozpoznávání obličeje, hlasoví asistenti a uživatelsky řízená personalizace, poskytují plynulý uživatelský zážitek a zároveň zlepšují zabezpečení prostřednictvím offline funkcí umělé inteligence.Takové pokroky snižují závislost na neustálém cloudovém připojení a podporují aplikace s lepší ochranou soukromí přizpůsobené individuálním preferencím.Kromě toho společné úsilí výrobců zařízení a inovátorů čipů nadále mění očekávání ohledně přístupné umělé inteligence v osobních technologiích.

Transformace v celém odvětví prostřednictvím strategické soutěže ASIC

Meteorický pokrok technologií ASIC zdůrazňuje zásadní posun v rámci globálních průmyslových odvětví.Rozvíjející se „AI Arms Race“ vidí hlavní hráče, kteří soupeří o konkurenční dominanci napříč doménami, jako jsou cloudové ekosystémy, autonomní stroje a spotřebitelská zařízení.Tato intenzita odráží jak krátkodobé ambice, tak dalekosáhlé strategie zaměřené na převrat v oblastech, jako je rozšířená realita, přesné monitorování životního prostředí a vznik propojené infrastruktury.Zatímco korporace zkoumají návrhy ASIC na míru, aby si vytvořily nové výklenky, důsledky přesahují ziskovost, podněcují výzvy a příležitosti, které předefinují synergii mezi člověkem a strojem.

Závěr

ASIC nadále předefinují moderní výpočetní techniku tím, že poskytují vysoký výkon, nízkou latenci a energetickou účinnost pro cílené aplikace.Jejich síla spočívá ve specializaci, díky čemuž jsou ideální pro odvození AI, edge computing a systémy v reálném čase, zatímco jejich omezení zahrnují vysoké náklady na vývoj a sníženou flexibilitu ve srovnání s GPU.Vzhledem k tomu, že průmyslová odvětví vyžadují rychlejší a efektivnější zpracování, inovace ASIC zůstávají zaměřeny na vyvážení výkonu, škálovatelnosti a energetické účinnosti.S neustálým pokrokem v metodách návrhu a architektury se očekává, že ASIC budou hrát roli při utváření budoucích technologií napříč mnoha sektory.

Často kladené otázky [FAQ]

1. Jaké jsou praktické aplikace čipů ASIC?

Čipy ASIC se používají v systémech, které potřebují vysokou rychlost a efektivitu pro konkrétní úlohu.Jsou běžné ve zpracování AI, zabezpečených datových systémech, mobilních zařízeních a automobilové elektronice.Pomáhají například urychlit zpracování dat v AI, zvládají šifrování v zabezpečených systémech, zlepšují zpracování signálu v chytrých telefonech a podporují radarové funkce v moderních vozidlech.Jejich cílený design jim umožňuje provádět tyto úkoly rychle a s nízkou spotřebou energie.

2. Jaké jsou hlavní rysy technologie čipů ASIC?

Technologie ASIC je známá tím, že je vysoce specializovaná a efektivní.Každý čip je navržen pro jeden účel, což mu umožňuje pracovat lépe než běžné procesory pro daný úkol.Odstraňuje nepotřebné funkce a zaměřuje se pouze na to, co je potřeba, což zvyšuje rychlost a snižuje spotřebu energie.Díky tomu jsou ASIC ideální pro aplikace, které vyžadují stabilní, konzistentní a optimalizovaný výkon.

3. Jak plní ASIC čipy své úkoly?

Čipy ASIC pracují pomocí pevných obvodů, které jsou navrženy při výrobě.Po sestavení dodržují nastavenou funkci a nelze je změnit.Tato pevná konstrukce jim umožňuje velmi efektivně plnit své úkoly, jako je zpracování dat AI nebo spouštění šifrovacích algoritmů.Protože nejsou flexibilní jako jiné procesory, zaměřují se na to, aby jednu práci zvládly velmi dobře s vysokou rychlostí a nízkou spotřebou energie.

Související blog

-

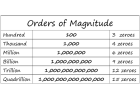

Kolik nul v milionu, miliardách, bilionu?

2024/07/29

Milion představuje 106, snadno pochopitelná postava ve srovnání s každodenními předměty nebo ročními platy. Miliarda, což odpovídá 109, z... -

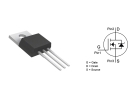

Datový list IRLZ44N MOSFET, obvod, ekvivalent, pineout

2024/08/28

IRLZ44N je široce používaný N-kanálový mosfet.Je známý svými vynikajícími schopnostmi přepínání, je vysoce vhodný pro mnoho aplikací,... -

Teplota baterie je příliš nízká, nabíjení se zastavilo.Jak to opravit?

2024/10/6

Problémy s nabíjení baterií mobilního telefonu jsou běžné, ale lze je efektivně spravovat.Teplota hraje velkou roli v účinnosti baterie, pr... -

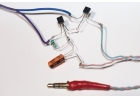

BC547 Transistor Comprehensive Guide

2024/07/4

Tranzistor BC547 se běžně používá v různých elektronických aplikacích, od základních signálních zesilovačů po komplexní obvody oscil... -

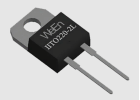

Komplexní průvodce pro SCR (usměrňovač ovládaného křemíkem)

2024/04/22

Křesťánové usměrňovače (SCR) nebo tyristory hrají klíčovou roli v technologii Power Electronics kvůli jejich výkonu a spolehlivosti.Tento ... -

Základy obvodů op-amp.

2023/12/28

Ve složitém světě elektroniky nás cesta do jejích tajemství vždy vede k kaleidoskopu komponent obvodů, jak vynikající, tak komplexní.V srd... -

LR621, SR621SW, 364, Ekvivalenty a náhrady baterie AG1

2024/07/15

Klapivé baterie LR621 a SR621SW převládají v kompaktních elektronických zařízeních, jako jsou hodinky, malé hračky, kalkulačky a odlehlé ... -

Porovnání rozdílů a aplikací NMOS a PMOS

2024/11/15

Pochopení rozdílů mezi tranzistory NMO a PMOS je důležité při navrhování účinných obvodů.NMOS (N-typ-typ-oxid-Semiconductor) a PMOS (p-ty... -

Co znamenají STD, AGM a GEL na nabíječce baterií

2024/07/10

Tradiční nabíječky baterií s olověným kyselinou jsou známé svou jednoduchostí a spolehlivostí.Svou účel efektivně slouží po celá lét... -

Kompletní průvodce multiplexery a jejich roli v digitálních systémech

2025/09/20

Multiplexery jsou komponenty v digitálních systémech, které jsou navrženy tak, aby nasměrovaly více vstupních signálů do jediného výstupn...

Hot Parts

- TAP227K006HSB

- AT1141MG

- ZL30155WE

- 12065C272JAT4A

- SC4809CIMSTR

- GJM0335C1E5R4BB01D

- A3P400-FGG256I

- ML7078B-01LA

- RT0402DRD0760K4L

- EC5462AR-G

- HD14069UBFPEL

- TAAD08JU21BCL-2A-DB

- DWM1000

- CY244V20ZZC-ES

- A3P125-PQG208I

- MDIN150H

- ISL32430EIBZ

- TSUM05PWJ-LF

- M58BW016DBT

- 04023A1R5DAT2A

- LTC1757A-1EMS8

- PCA9518PWR

- T491A156K004AT

- SKM300GB125D

- RT0402DRE07115KL

- GRM0335C1H8R4CA01D

- LD051C332KAB4A

- XC3S1600E-4FG400I

- W29C011P-90

- 6MBP20RTA060-01

- LTC4012IUF-2#PBF

- LH1780BAR

- GQM1555C2D5R2BB01D

- INA132UA

- LT1120IS8

- GCM155R71H683KE02J

- VI-26D-CU

- E48SC32009NRDH

- VE-2W0-IY

- CRC4A012840

- K4S561632D-TP75

- S553-5999-F5

- GRM188R60J225KE01D

- B50612EB1KMLG-P21

- PM7311-BGI

- TR250-180U-T

- TMX320AV7110GFN

- KZ4E053311CFP

- EDW4032BABG-60-F-R

- ADSP-BF561SKB600